## S2 DUT GEii1 - Module SEI

# **TDAD\_ECH: Echantillonnage & Chaine TNS**

Me 22 avril 2020

Sujet: **9h30** Correction: Indications **()** horaire

# Exercice 1 : Les bases de l'échantillonnage

**(10h)**

Dans le cadre du réseau téléphonique commuté (RTC) classique, on échantillonne les signaux de communications à une fréquence Fe de 8kHz.

Q1: On suppose que l'on transmet un signal sinusoïdal de fréquence 1kHz et d'amplitude 2Vpp. Représenter avec précision l'allure du signal échantillonné idéal en fonction du temps. Tracer l'allure de son spectre.

Q2: On conserve les mêmes grandeurs qu'à la question précédente mais l'on considère cette fois le signal échantillonné bloqué. Représenter avec précision l'allure du signal échantillonné bloqué en fonction du temps et tracer l'allure de son spectre.

Q3: Rappeler le théorème de Shannon relatif à l'échantillonnage des signaux. Quelle règle doit-on appliquer pour les signaux de communications du réseau téléphonique commuté ?

**Q4:** Si l'on ne respecte pas la règle relative à l'échantillonnage des signaux, que se passet-il? Quel élément doit-on utiliser dans la chaine d'acquisition pour s'affranchir de ce problème?

**Q5:** En pratique on limite la bande passante des signaux téléphonique à une fréquence de 3400Hz. Quelle est la raison de cette limite?

On connecte un signal sinusoïdal symétrique de fréquence 12kHz sur un oscilloscope numérique TDS2014B que l'on utilise couramment dans les salles de travaux pratiques et l'on effectue une analyse FFT.

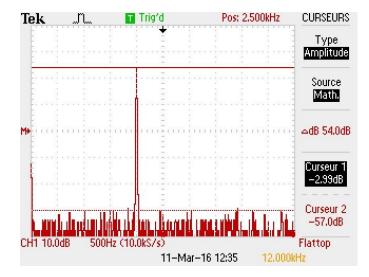

**Q1 :** A partir des indications fournies sur la figure suivante, quelle est la valeur de la fréquence d'échantillonnage ? Justifier l'unité utilisée.

**Q2 :** Si l'on ne tient pas compte de la fréquence du signal d'entrée indiquée en bas de la figure, quelle fréquence mesure-t-on à partir de la simple analyse FFT ? Que se passe-t-il ? Justifier ce résultat.

## Exercice 3 : Mise en œuvre du circuit ISD2500

() 10h50

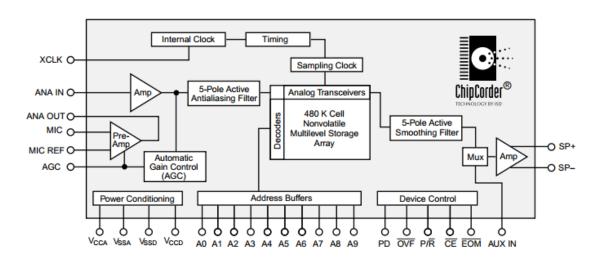

**Q1 :** Pour une application audio on vous propose de mettre en œuvre le circuit ISD2500 dont un extrait de documentation constructeur est proposé sur la page suivante. Quelle est la fonction de ce circuit ?

**Q2:** Rappeler le théorème de Shannon relatif à l'échantillonnage des signaux. Justifier le rapport qui existe entre les valeurs données dans la colonne « **Input Sample Rate** » et la colonne « **Typical Filter** » dans le tableau

**Q3:** Si l'on ne respecte pas la règle relative à l'échantillonnage des signaux, que se passet-il ? Quel élément est présent dans le circuit pour s'affranchir de ce problème ?

**Q4:** Pour quelle raison la durée d'enregistrement est liée à la qualité des signaux ? Justifier le lien qui existe entre la durée et la fréquence d'échantillonnage.

**Q5**: On sélectionne le circuit ISD2575 et l'on suppose que l'on enregistre un signal sinusoïdal de fréquence 800Hz. Quel est le nombre d'échantillons obtenus pour une période ? Représenter avec précision le signal échantillonné idéal en fonction du temps. Tracer l'allure de son spectre en précisant clairement l'échelle des fréquences.

**Q6:** On conserve les mêmes grandeurs qu'à la question précédente mais l'on considère cette fois le signal échantillonné bloqué obtenu à la sortie du CNA (« analog transceiver » sur le schéma bloc). Représenter avec précision l'allure du signal échantillonné bloqué en fonction du temps et tracer l'allure de son spectre.

**Q7:** Pour quelle raison retrouve-t-on un filtre en sortie du CNA (« analog transceiver »)? Quel est le nom de ce filtre (en français)?

### ISD2500 Series

Single-Chip Voice Record/Playback Devices 32-\*, 40-\*, 48-\*, 64-\*, 60-, 75-, 90-, and 120-Second Durations

#### **FEATURES**

- Easy-to-use single-chip voice Record/ Playback solution

- High-quality, natural voice/audio reproduction

- Manual switch or microcontroller compatible Playback can be edge- or levelactivated

- Single-chip durations of 32\*, 40\*, 48\*, 64\*, 60, 75, 90, and 120 seconds

- · Directly cascadable for longer durations

- Automatic Power-Down (Push-Button Mode)

- Standby current 1 μA (typical)

- Zero-power message storage

- Eliminates battery backup circuits

- Fully addressable to handle multiple messages

- 100-year message retention (typical)

- 100,000 record cycles (typical)

- · On-chip clock source

- · No algorithm development required

- Single +5 volt power supply

#### GENERAL DESCRIPTION

Information Storage Devices' ISD2500 Chip-Corder® Series provides high-quality, single-chip Record/Playback solutions for 32- to 120-second messaging applications. The CMOS devices include an on-chip oscillator, microphone preamplifier, automatic gain control, antialiasing filter, smoothing filter, speaker amplifier, and high density multi-level storage array. In addition, the ISD2500 is microcontroller compatible, allowing complex messaging and addressing to be achieved.

Recordings are stored in on-chip nonvolatile memory cells, providing zero-power message storage. This unique, single-chip solution is made possible through ISD's patented multilevel storage technology. Voice and audio signals are stored directly into memory in their natural form, providing high-quality, solid-state voice reproduction.

#### ISD2500 SERIES SUMMARY

| Part<br>Number | Duration<br>(Seconds) | Input Sample<br>Rate (KHz) | Typical Filter<br>Pass Band (KHz) |

|----------------|-----------------------|----------------------------|-----------------------------------|

| ISD2560        | 60                    | 8.0                        | 3.4                               |

| ISD2575        | 75                    | 6.4                        | 2.7                               |

| ISD2590        | 90                    | 5.3                        | 2.3                               |

| ISD25120       | 120                   | 4.0                        | 1.7                               |

| ISD2532*       | 32                    | 8.0                        | 3.4                               |

| ISD2540*       | 40                    | 6.4                        | 2.7                               |

| ISD2548*       | 48                    | 5.3                        | 2.3                               |

| ISD2564*       | 64                    | 4.0                        | 1.7                               |

#### DETAILED DESCRIPTION

#### Speech/Sound Quality

The ISD2500 Series includes devices offered at 4.0, 5.3, 6.4, and 8.0 KHz sampling frequencies, allowing the user a choice of speech quality options. Increasing the duration within a product series decreases the sampling frequency and bandwidth, which affects sound quality. Please refer to the ISD2500 Series Summary table on page 1-79 to compare filter pass band and product durations.

The speech samples are stored directly into onchip nonvolatile memory without the digitization and compression associated with other solutions. Direct analog storage provides a very true, natural sounding reproduction of voice, music, tones, and sound effects not available with most solid-state digital solutions.

#### Duration

To meet end system requirements, the ISD2500 Series offers single-chip solutions at  $32^*$ ,  $40^*$ ,  $48^*$ ,  $64^*$ , 60, 75, 90, and 120 seconds. Parts may also be cascaded together for longer durations.

#### ISD2560/75/90/120 DEVICE BLOCK DIAGRAM

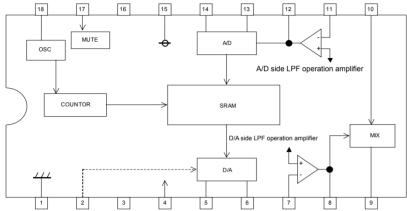

On vous propose l'étude du circuit BU9253 dont un extrait de documentation constructeur est donné ci-contre. Il s'agit d'un circuit permettant de réaliser un système d'écho pour un signal audio utilisé par exemple pour un Karaoké.

Le signal audio est échantillonné à une fréquence correspondant à la fréquence d'horloge du circuit divisée par 6. Ce signal est alors numérisé et stocké dans une mémoire (SRAM) et restitué sur un convertisseur numérique analogique en sortie.

#### Features

BU9253AS/FS has functions required by Karaoke echo system

- 1) Digital delay time: 131ms (fclk = 375kHz) Sample frequency = clock frequency ÷ 6

- 2) Built-in mixing circuit for adding original sound and echo sound

- 3) Echo mix ratio settable by DC voltage

- 4) Built-in amplifier circuit for structuring input/output secondary LPF

- 5) Microphone mute function (mute of mixing sound of original sound + echo sound)

- 6) Built-in CR oscillation circuit

Le signal ainsi retardé et le signal original sont injectés dans un sommateur réglable (MIX) afin de créer l'effet audio voulu.

**Q1 :** A partir des informations données sur l'extrait, déterminer la valeur de la fréquence d'échantillonnage Fe de ce circuit.

**Q2 :** En déduire la taille de la mémoire nécessaire pour obtenir la valeur du délai indiquée dans la documentation.

**Q3**: L'amplificateur opérationnel (bornes 12 & 11) que l'on retrouve à l'entrée du convertisseur A/D permet de réaliser avec quelques composants externe un filtre passe bas du 2nd ordre dont on fixe la fréquence de coupure à 3,4kHz (on fixe m=0,707). Quel est le rôle de ce filtre et quel est son nom ? Donner également son nom en anglais.

**Q4 :** Quelle est l'atténuation apportée par ce filtre pour la valeur de fréquence Fe/2 ? Commentez le résultat obtenu.

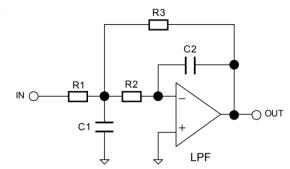

En sortie du convertisseur D/A, le constructeur propose de mettre en œuvre le filtre ci-contre et pour lequel on donne la fonction de transfert suivante :

$$\frac{V_{OUT}(j\omega)}{V_{IN}(j\omega)} = -\frac{R3}{R1} \cdot \frac{1}{1 + \left(1 + \frac{R3}{R1} + \frac{R3}{R2}\right) jR2C2\omega + R2.R3.C1.C2\left(j\omega\right)^2}$$

**Q5 :** Quel est le nom de ce filtre en français et en anglais ? Préciser son rôle.

Dans le schéma d'application le constructeur donne les valeurs suivantes : R1=11k $\Omega$  R2=7,5k $\Omega$  R3=22k $\Omega$  C1=6.8nF C2=1nF

**Q6 :** Déterminer le gain maximum de ce filtre (en dB), sa fréquence propre et son coefficient d'amortissement. Vous donnerez les expressions et vous effectuerez les applications numériques correspondantes. Commentez les résultats obtenus.

On souhaite mettre en œuvre le circuit MAX270.

Vous répondrez aux questions en vous appuyant sur les données fournies ainsi que sur VOS connaissances en matière de filtrage électrique.

**Q1 :** Quelle est la fonction et la particularité de ces circuits ?

**Q2:** Dans quelles applications peut-on utiliser idéalement ces circuits?

# MAX270/MAX271 Digitally-Programmed, Dual 2nd-Order Continuous Lowpass Filter

#### **General Description**

The MAX270/MAX271 are digitally-programmed, dual second-order continuous-time lowpass filters. Their typical dynamic range of 96dB surpasses most switched capacitor filters which require additional filtering to remove clock noise. The MAX270/MAX271 are ideal for anti-aliasing and DAC smoothing applications and can be cascaded for higher-order responses.

The two filter sections are independently programmable by either microprocessor ( $\mu P$ ) control or pin strapping. Cutoff frequencies in the 1kHz to 25kHz range can be selected.

The MAX270 has an on-board, uncommitted op amp, while the MAX271 has an internal track-and-hold (T/H).

# Filter Programming Cutoff Frequency

fc is the frequency of 3dB attenuation in the filter response.

The equations for calculating  $f_{\hbox{\scriptsize C}}$  from the programmed code are as follows:

$$f_C = \frac{87.5}{87.5 - \text{CODE}} \times \text{1kHz}$$

for codes 0 - 63

( $f_C = \text{1kHz} \text{ to 3.57kHz}$ )

$$f_C = \frac{262.5}{137.5 - CODE} \times 1kHz$$

for codes 64 - 127 ( $f_C = 3.57kHz \text{ to } 25kHz$ )

where CODE is the data on pins D0-D6 (0-127). D6 is the most significant bit (MSB).

#### **Features**

- ♦ Continuous-Time Filtering No Clock Required

- ♦ Dual 2nd-Order Lowpass Filters

- Sections Independently Programmable: 1kHz to 25kHz

- ♦ 96dB Dynamic Range

- ♦ No External Components

- ♦ Cascadable for Higher Order

- ♦ Low-Power Shutdown Mode

- ◆ Track-and-Hold (MAX271)

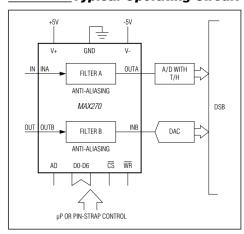

#### **Typical Operating Circuit**

**Q3 :** Le schéma d'application proposé par le constructeur comporte plusieurs erreurs. Quelles sont les corrections que vous apporteriez à ce schéma ?

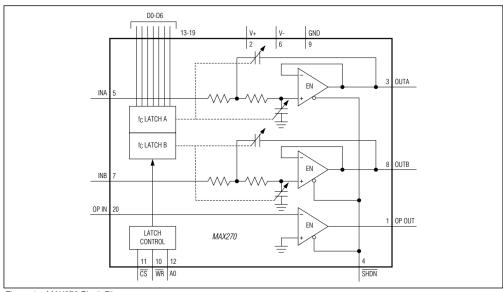

Figure 1a. MAX270 Block Diagram

**Q4 :** Quelle est la structure retenue pour la réalisation des filtres et représentée sur le schéma synoptique du circuit MAX270 ? Quelles sont les éléments qui permettent le réglage de la fréquence de coupure ?

**Q5**: On désire utiliser ce circuit pour une opération de filtrage audio avec une fréquence de coupure de 5kHz. Quelle doit-être la valeur du code à appliquer sur les bornes D0 à D6 ?