# Synthèse de fréquence, Bruit électrique & Transmission numérique

## CORRECTION ECLAIR

### Exercice n°1 : Analyseur de spectre & Bruit

[5pts]

**Q1** : La densité spectrale de puissance est une quantité qui traduit la répartition de la puissance du signal d'un point de vue fréquentiel. On parle de bruit blanc lorsque la DSP est constante sur une grande plage de fréquence.

**Q2** :  $B_{eff} = \sqrt{4kT.R_{eq}} = 49,8\mu V$  **Q3** :  $P_{dBm} = 10 \cdot \log\left(\frac{U_{eff}^2}{R \cdot 1mW}\right) = 10 \cdot \log\left(\frac{4kT \cdot ResBW}{1mW}\right) = -107,8dBm$

**Q4** : Le plancher de bruit se situe à -70dBm ce qui est un niveau très supérieur à celui du seuil bruit thermique. Ce n'est donc pas le bruit dû à la résistance d'entrée et il s'agit du bruit interne dont on peut trouver le niveau

de densité spectrale en écrivant :  $P_{dBm} = 10 \cdot \log\left(\frac{Do \cdot ResBW}{R \cdot 1mW}\right)$  soit  $Do = \frac{R \cdot 1mW}{ResBW} \cdot 10^{\frac{P_{dBm}}{10}} = 5 \cdot 10^{-15} V^2/Hz$

**Q5** : Pour un filtre de résolution 1kHz le plancher de bruit sera à -100dBm

### Exercice n°2 : Les codages mis en œuvre dans les interfaces PC

[5pts]

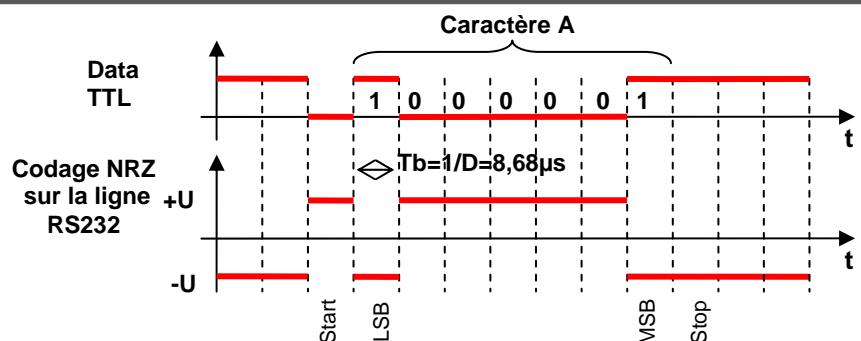

**Q1** : Dans le cas de la liaison série RS232 le bit 1 est codé par un niveau égal à -U et le bit 0 est codé par un niveau égal à +U.

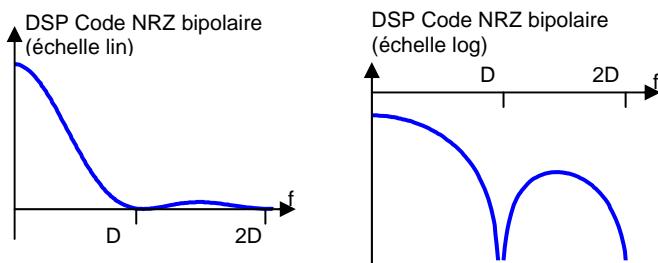

**Q2** :

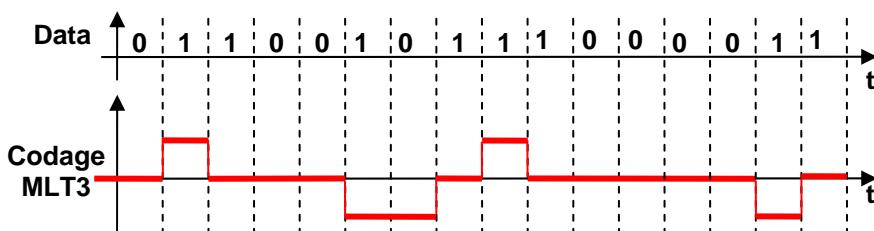

**Q3 : Codage MLT3**

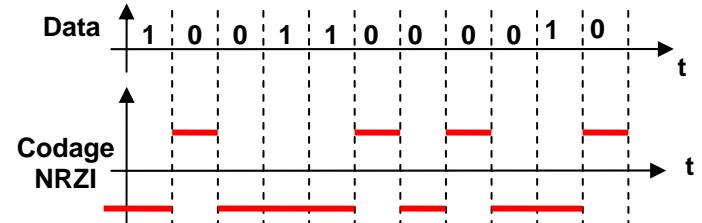

**Q4 : Codage NRZI.**

### Exercice n°3 : La relation de Shannon Hartley pour une ligne spécialisée

[4pts]

**Q1** : Relation de Shannon Hartley :

$$D_{max} = BP \cdot \log_2 \left( 1 + \frac{S}{B} \right)$$

D<sub>max</sub> : Débit maximum

BP : Bande passante du canal de transmission

S : Puissance du signal utile B : Puissance du bruit

$$Q2 : DUP_{max} = 2 \times 4k \times \frac{\log\left(1 + 10^{\frac{35}{10}}\right)}{\log(2)} = 93 \text{ kbit/s} \quad Q3 : DUP_{max} = D3_{max} + D4_{max} + D5_{max}$$

$$D3_{max} = D4_{max} = 4k \times \frac{\log\left(1 + 10^{\frac{30}{10}}\right)}{\log(2)} = 39,87 \text{ kbit/s} \text{ soit } D5_{max} = 13,26 \text{ kbit/s}$$

$$\text{donc } \left| \frac{S}{B} \right|_5 = 2^{\frac{D5_{max}}{BP}} - 1 = 8,95 = 9,52 \text{ dB}$$

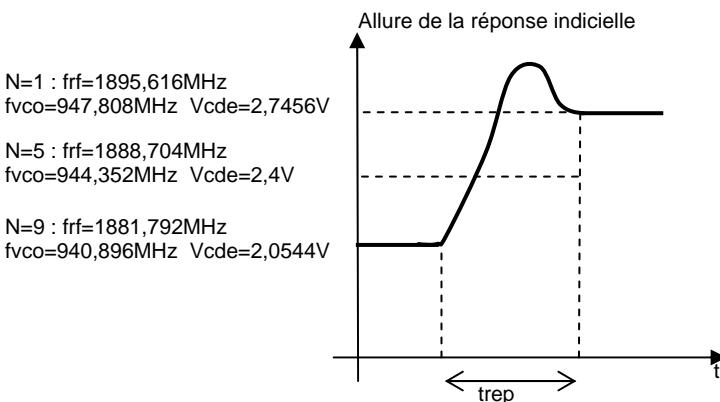

### Problème : Synthèse de fréquence pour un téléphone DECT [15pts]

**Q1 :** Le VCO seul ne permet pas de garantir une bonne stabilité de la fréquence porteuse. La synthèse de fréquence permet à la fois d'obtenir une grande stabilité et une grande précision sur la valeur de la fréquence porteuse tout en permettant un réglage de celle-ci afin d'obtenir les 10 valeurs correspondants aux 10 canaux.

**Q2 :** Le sommateur sur l'entrée du VCO permet de réaliser une modulation de fréquence à partir de l'entrée TXDATA.

**Q3 :**  $Fr_f = 2 \cdot N \cdot F_{xtal} / R$     **Q4 :**  $F_{xtal} = 13,824 \text{ MHz}$  ou  $F_{xtal} = 10,368 \text{ MHz}$   $R = 16$  ou  $R = 12$

La fréquence de travail du comp de phase =  $13,824 \text{ MHz} / 16 = 10,368 \text{ MHz} / 12 = 864 \text{ kHz}$

**Q5 :** canal n°5 en émission  $\Rightarrow Fr_f = 1888,704 \text{ MHz} \Rightarrow N = 1093$     **Q6 :** Voir poly de cours  $I_o = 1 \text{ mA}$

$$Q7: Z_{eq}(p) = \frac{R_5}{1 + R_5 \cdot C_{11} \cdot p} + \frac{1}{C_{12} \cdot p} = \frac{1}{C_{12} \cdot p} \cdot \frac{1 + R_5 \cdot (C_{11} + C_{12}) \cdot p}{1 + R_5 \cdot C_{11} \cdot p} \text{ de la forme indiquée } Z_{eq}(p) = \frac{1}{C_{12} \cdot p} \cdot \frac{1 + \frac{p}{\omega_1}}{1 + \frac{p}{\omega_2}}$$

$$\text{avec } \omega_2 = \frac{1}{R_5 C_{11}} \text{ et } \omega_1 = \frac{1}{R_5 (C_{11} + C_{12})}$$

**Q8:** Le calcul de la FTBO ne doit prendre en compte que les éléments dans la boucle donc :

$$FTBO(p) = \frac{2\pi K_{CP}}{p} \cdot \frac{1}{C_{12} \cdot p} \cdot \frac{1 + \frac{p}{\omega_1}}{1 + \frac{p}{\omega_2}} \cdot \frac{K_{VCO}}{N} \text{ de la forme indiquée } FTBO(p) = \left( \frac{\omega_1}{p} \right)^2 \cdot \frac{1 + \frac{p}{\omega_1}}{1 + \frac{p}{\omega_2}} \text{ avec } \omega_i = \sqrt{\frac{2\pi K_{CP} \cdot K_{VCO}}{N \cdot C_{12}}}$$

**Q9:**  $M\varphi = 2 \cdot \arctan\left(\sqrt{1 + \frac{C_{12}}{C_{11}}}\right) - \frac{\pi}{2}$     **Q10:**  $R_5 = 6,8 \text{ k}\Omega$   $C_{11} = 330 \text{ pF}$   $C_{12} = 1 \text{ nF}$  (le condensateur de  $6,8 \text{ pF}$  n'est là que pour assurer un comportement capacitif pour les hautes fréquences)

**Q10:**  $M\varphi = 37^\circ$  donc la boucle est stable    **Q12:** Il s'agit d'un circuit LC accordé utilisant des diodes varicap

**Q13:**  $\omega_1 = 445,633 \text{ krad/s}$      $\omega_2 = 110,57 \text{ krad/s}$     donc  $f_t = 35,33 \text{ kHz}$  (suffisamment lent devant le rythme binaire pour que la PLL ne réagisse pas aux variations de l'entrée TXDATA)

**Q14:** temps de réponse =  $1/f_t \approx 28 \mu\text{s}$